企业名称:

联系人:

电话:

手机:

邮箱:

传真:

地址:

网址 : www.micro-graph.com.cn

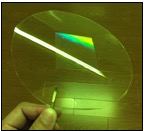

光刻加工(Photolithography)是半导体制造、微机电系统(MEMS)、印刷电路板(PCB)等精密制造领域的核心技术之一,其原理是通过光线(如紫外线、极紫外光EUV等)照射,将掩膜版(Mask)上的图案转移到涂有光刻胶的基板表面,从而实现微米级甚至纳米级图形的精确加工。以下是关于光刻加工的详细解析: 一、光刻加工的核心流程 光刻工艺通常包括以下关键步骤,以半导体芯片制造为例: 1. 基板预处理 清洗:去除基板(如硅片)表面的污染物(颗粒、有机物、金属离子等),常用湿法清洗(硫酸/双氧水混合液)或干法清洗(等离子体处理)。 干燥:确保表面无水分,避免影响后续光刻胶附着力。 涂底膜:在基板表面涂覆附着力促进剂(如六甲基二硅氮烷,HMDS),增强光刻胶与基板的结合力。 2. 涂胶(Spin Coating) 通过旋转涂胶机将液态光刻胶均匀涂覆在基板表面,形成厚度可控的胶膜(通常为几百纳米至几微米)。 关键参数:旋转速度(转速越高,胶层越薄)、光刻胶粘度、旋转时间。 3. 前烘(Soft Bake) 加热基板(通常在80~120℃),蒸发光刻胶中的溶剂,增强胶膜硬度和附着力,同时减少后续曝光时的扩散效应。 设备:热板或烘箱。 4. 曝光(Exposure) 利用光刻机将掩膜版上的图案通过光线投影到光刻胶上,使光刻胶发生化学变化(光化学反应)。 分类: 正性光刻胶:曝光区域在显影后溶解,形成与掩膜版相同的图案; 负性光刻胶:曝光区域在显影后保留,形成与掩膜版相反的图案。 光源波长:波长越短,分辨率越高(如EUV光刻使用13.5nm极紫外光,可实现3nm以下制程)。 5. 显影(Development) 使用显影液溶解曝光后光刻胶的可溶部分,形成与掩膜版对应的三维图案。 关键控制:显影时间、显影液浓度,避免过显影或欠显影导致图案失真。 6. 后烘(Hard Bake) 高温烘烤(120~180℃)固化光刻胶图案,增强其抗刻蚀或离子注入的能力。 作用:减少光刻胶在后续工艺中的膨胀或脱落。 7. 图形转移(Etching/Ion Implantation) 刻蚀:以光刻胶为掩膜,通过干法刻蚀(等离子体刻蚀)或湿法刻蚀(化学腐蚀)将图案转移到基板表面的材料层(如氧化层、金属层)。 离子注入:利用光刻胶遮挡,将特定离子(如磷、硼)注入基板指定区域,改变半导体电学特性。 8. 去胶(Strip) 去除完成图形转移后的残留光刻胶,常用湿法(强酸/强碱溶液)或干法(氧等离子体灰化)。 二、关键技术与挑战 为工艺常数(理想情况下接近0.25)。 挑战:随着制程缩小(如从7nm到3nm),需不断缩短光源波长(如从深紫外DUV升级到极紫外EUV),或采用多重曝光技术(如SAQP自对准四重图案化)。 2. 套刻精度(Overlay Accuracy) 多层光刻时,要求新层图案与底层图案精确对准(误差需控制在纳米级),否则会导致器件短路或失效。 解决方案:光刻机配备高精度对准系统(如激光干涉仪、图像识别算法),并通过工艺监控(如套刻标记检测)实时调整。 3. 光刻胶性能 要求:高灵敏度(低曝光能量)、高分辨率、低缺陷率、强抗刻蚀性。 发展趋势:研发化学增幅型光刻胶(CAR)、纳米压印光刻胶(NIL)等新型材料,以适应更小线宽需求。 4. 缺陷控制 光刻过程中微小颗粒(如灰尘、光刻胶残渣)可能导致图案缺陷,影响芯片良率。 应对措施:在超净间(Class 100级)中操作,采用扫描电子显微镜(SEM)检测缺陷,通过激光修复技术消除掩膜版缺陷。 三、主要应用领域 半导体制造 用于制造晶体管、互连线路、存储单元等器件,是芯片制程(如5nm、3nm)的核心工艺。 案例:EUV光刻技术被用于台积电3nm、三星3nm及Intel 4nm工艺节点。 微机电系统(MEMS) 制造加速度计、陀螺仪、微传感器等器件,例如通过深反应离子刻蚀(DRIE)结合光刻技术加工硅基三维结构。 印刷电路板(PCB) 在电路板上刻蚀导电线路,实现元件互连,常用紫外光刻技术(波长365nm)。 光电子与光学器件 制作光波导、衍射光学元件(DOE)、微透镜阵列等,例如AR/VR设备中的光学元件加工。 纳米技术 纳米光刻技术(如电子束光刻EBL、聚焦离子束FIB)用于制备纳米线、量子点等结构,分辨率可达亚10nm级别。 四、光刻技术的发展方向 极紫外光刻(EUV) 波长13.5nm,已用于7nm以下制程芯片制造,解决DUV多重曝光的复杂性问题。 纳米压印光刻(NIL) 通过模具压印而非曝光实现图案转移,成本低、效率高,适合大面积纳米图案制造(如存储芯片、光学器件)。 定向自组装(DSA) 利用高分子材料自组装特性辅助光刻,降低线宽粗糙度(LWR),提升图案均匀性。 电子束光刻(EBL) 分辨率可达亚纳米级,主要用于科研和掩膜版制作,但速度较慢(逐点扫描),不适合大规模量产。 X射线光刻与粒子束光刻 探索更短波长光源(如X射线)或离子束、电子束直写技术,突破光学光刻物理极限。 五、典型设备与厂商 光刻机: ASML(荷兰):全球唯一量产EUV光刻机的厂商,代表机型NXE:3400B(EUV)、TWINSCAN NXE:3400B(DUV)。 尼康/佳能(日本):主要提供DUV光刻机,用于成熟制程(如28nm及以上)。 涂胶/显影设备: 东京电子(TEL)、DNS(Disco):提供全自动涂胶-显影机,与光刻机联机作业(Track-Exposure Integration)。 量测设备: 科磊(KLA):提供光学关键尺寸量测(OCD)、缺陷检测设备,确保光刻图案精度。 总结 光刻加工是现代精密制造的“心脏”技术,其精度和效率直接决定了芯片、MEMS等器件的性能与成本。随着半导体行业向3nm及以下制程迈进,EUV光刻、纳米压印等新技术正不断突破物理极限,而缺陷控制、套刻精度等挑战仍需通过材料、设备和工艺的协同创新来解决。未来,光刻技术将继续在摩尔定律延续和超越摩尔领域中扮演核心角色。 介绍一下光刻加工技术的发展历程 光刻加工技术的发展历程大致如下1: 早期探索阶段(20 世纪 40 年代末 - 60 年代):1947 年贝尔实验室发明第一只点接触晶体管,光刻技术开始发展。当时计算机大量使用使芯片需求大增,光刻技术受到重视。50 年代光刻技术 “百花齐放”,出现多种光刻手段,但分辨率要求不高,器件也较简单。1959 年第一台晶体管计算机出现,仙童半导体提出规范的光刻工艺,并研制出世界第一个适用单结构硅晶片。60 年代,光刻技术从实验室走向生产线,仙童提出 CMOS IC 制造工艺,GCA 公司开发出光学图形发生器和分布重复精缩机。 接触式与接近式光刻时代(20 世纪 60 年代 - 70 年代):20 世纪 60 年代,接触式光刻技术成为小规模集成电路时期主要光刻技术,掩膜版与晶圆表面光刻胶直接接触,分辨率可达亚微米级,但存在晶圆与掩膜版摩擦易形成划痕、产生颗粒沾污等问题,导致晶圆良率及掩膜版使用寿命降低。70 年代,接近式光刻技术广泛应用,掩膜版与晶圆光刻胶不直接接触,留有被氮气填充的间隙,解决了接触式光刻的部分问题。这一时期,微光刻技术基本成熟,以 8μm 工艺为代表,GCA 公司开发出第一台分布重复投影曝光机,使集成电路图形线宽从 1.5μm 缩小到 0.5μm 节点。 投影光刻技术发展阶段(20 世纪 70 年代中后期 - 90 年代):70 年代中后期出现投影光刻技术,基于远场傅里叶光学成像原理,在掩膜版和光刻胶之间采用具有缩小倍率的投影成像物镜,有效提高了分辨率。80 年代,美国 SVGL 公司开发出第一代步进扫描投影曝光机,集成电路图形线宽从 0.5μm 缩小到 0.35μm 节点,光刻集成电路进入自动化大生产时期,进入超大规模集成电路时代,CMOS 工艺晶体管数量大幅增加。90 年代,高分辨光刻技术的特征尺寸向深亚微米推进,蔡司、尼康等公司纷纷推出自己的投影式光刻产品,1999 年实现了 0.13μm 光刻工艺。 纳米光刻时代(21 世纪初 - 至今):2002 年,台积电提出 193nm 浸润式光刻技术,ASML 与台积电合作,于 2004 年推出浸没式光刻机,凭借优良性价比使 ASML 市场份额大幅提高。2002 年,荷兰 ASML 公司推出第一款极紫外线(EUV)光刻机,可实现更高分辨率和更小线宽,最小曝光线宽达 14 纳米,使芯片制造技术迎来质的飞跃。随着制程演进,EUV 光刻机不断发展,目前最先进的 EUV 光刻机曝光分辨率为 13 纳米,可用于 3nm 制程芯片的生产。同时,其他新型纳米光刻技术如电子束光刻技术、纳米压印技术等也在不断发展,纳米压印技术近年来取得进展,佳能宣布推出可制造 5nm 芯片的纳米压印半导体制造设备,电子束光刻技术也在不断探索中,形成了多种光刻技术相互补充的格局。